October 2005

#### **■**General Description

Combining low-power CMOS logic with high-current, high-voltage power FET outputs, the Series SLA705xM translator/driver provides complete control and drive for a two-phase unipolar stepper motor with internal fixed off time, pulse-width modulation (PWM) control of the output current in a power multi-chip module (PMCM<sup>TM</sup>). The CMOS logic section provides the sequencing logic, direction,

full/half-step control, synchronous/asynchronous PWM operation, and a "sleep" function. The minimum CLOCK input is an ideal fit for applications where a complex  $\mu P$  is unavailable or overburdened. TTL or LSTTL may require the use of appropriate pull-up resistors to ensure a proper input-logic high. For PWM current control, the maximum output current is determined by the user's selection of a reference voltage and sensing resistor. The NMOS outputs are capable of sinking up to 1,2 or 3 A and withstanding 46 V in the off state. Ground-clamp and flyback diodes provide protection against inductive transients. Special power-up sequencing is not required. Full-step (2 phase) and half-step operation are externally selectable. Two-phase drive energizes two adiacent phases in each detent

Full-step (2 phase) and half-step operation are externally selectable. Two-phase drive energizes two adjacent phases in each detent position (AB-BC-CD-DA). This sequence mode offers an improved torquespeed product, greater detent torque, and is less susceptable to motor resonance. Half-step excitation alternates between the one-phase and two-phase modes (A-AB-B-BC-C-CD D-DA), providing an eight-step sequence.

#### **■**Applications

- $\bullet$ PPC

- Printer

- OA Equipment

#### **■**Features

- To 3A Output Rating

- •Internal Sequencer for Full or Half-Step Operation

- ●PWM Constant-Current Motor Drive

- •Cost-Effective, Multi-Chip Solution

- •100 V, Avalanche-Rated NMOS

- •Low rDS(on) NMOS Outputs (300 milli-ohms typical)

- •Advanced, Improved Body Diodes

- •Half-Step and Full-Step Unipolar Drive

- •Inputs Compatible with 3.3 V or 5 V Control Signals

- •Sleep Mode

- Internal Clamp Diodes

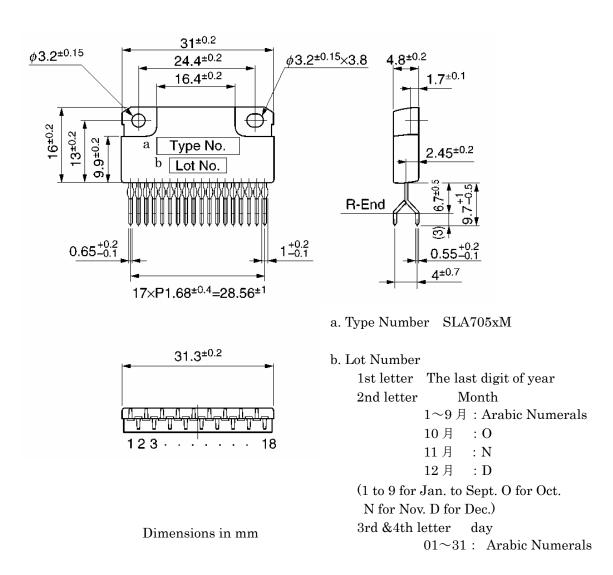

#### ■Package----SLA18Pin

#### **■Key Specifications**

Motor Supply Voltage (VM): 44V max

Load Supply Voltage (Vs): 10V~44V

Logic Supply Voltage (Vcc): 3V~5.5V

•Output Current (Io): 1A(SLA7050M)

2A(SLA7051M) 3A(SLA7052M)

•Output Maximum Voltage (V<sub>DSS</sub>): 100V min

October 2005

### Scope

The present specifications shall apply to Sanken 2 Phase Stepper Motor Driver IC, SLA705xM Series. The present specifications shall apply to SLA 705xM Series which is performed RoHS instructions.

### **Outline**

| Туре         | Hybrid integrated circuit                                                      |

|--------------|--------------------------------------------------------------------------------|

| Structure    | Plastic molded (transfer mold)                                                 |

| Applications | To drive a 2 phase stepper motor.<br>(Full or Half Step. PWM Current Control.) |

### Absolute maximum ratings

| Characteristic                 | Symbol           | Ratings               | Unit                   | Remarks                    |

|--------------------------------|------------------|-----------------------|------------------------|----------------------------|

| Motor Supply Voltage           | VM               | 46                    | V                      |                            |

| Load Supply Voltage            | Vs               | 46                    | V                      |                            |

| Logic Supply Voltage           | Vec              | 7                     | V                      |                            |

|                                |                  | 1.0                   |                        | SLA7050M                   |

| Output Current                 | Io               | 2.0                   | A                      | SLA7051M                   |

|                                |                  | 3.0                   |                        | SLA7052M                   |

| Logic Input Voltage            | Vin              | $-0.3 \sim Vec + 0.3$ | V                      |                            |

| REF Input Voltage              | VREF             | $-0.3 \sim Vec + 0.3$ | V                      |                            |

| Sense Voltage                  | VRs              | -2~2                  | V                      | Tw<1µS doesn't contain it. |

| Total Device Dissipation       | D <sub>rs</sub>  | 4                     | W                      | at Ta=25℃                  |

| Total Bevice Bissipation       | $P_{\mathrm{D}}$ | 20                    | W                      | at Tc=25℃                  |

| Junction Temperature           | Tj               | 150                   | $^{\circ}$ C           |                            |

| Operating Temperature<br>Range | Ta               | $-20 \sim 85$         | $^{\circ}$ C           |                            |

| Storage Temperature Range      | Tstg             | $-30\sim150$          | $^{\circ}\!\mathbb{C}$ |                            |

October 2005

### **Electrical characteristics**

### Recommendable Operating Range

| Characteristic       | Symbol | Ratings |     | Unit         | Remarks                                                 |  |

|----------------------|--------|---------|-----|--------------|---------------------------------------------------------|--|

| Characteristic       | Symbol | MIN     | MAX | Onit         | ivemarks                                                |  |

| Motor Supply Voltage | VM     |         | 44  | V            |                                                         |  |

| Load Supply Voltage  | Vs     | 10      | 44  | V            |                                                         |  |

| Logic Supply Voltage | Vcc    | 3.0     | 5.5 | V            | Please adjust the Vcc surge voltage to 0.5V or less.    |  |

| REF Input Voltage    | VREF   | 0.1     | 1.0 | V            | The control current accuracy decreases in 0.1V or less. |  |

| Package Temperature  | Тс     |         | 100 | $^{\circ}$ C | 10Pin temperature<br>(at No Fin)                        |  |

### Electrical Characteristic (Ta=25°C,Vs=24V,Vcc=5V Unless Otherwise Noted)

| Characteristic            | Symbol  | Limits  |              |          | Unit             | Test Condition             |

|---------------------------|---------|---------|--------------|----------|------------------|----------------------------|

| Characteristic            | Symbol  | MIN     | TYP          | MAX      | Offic            | lest Condition             |

| Load Supply Current       | Is      |         |              | 15       | mA               | Regularity                 |

| Load Supply Current       | Iss     |         |              | 100      | $\mu$ A          | at SLEEP operates          |

| Logic Supply Current      | Iœ      |         |              | 3        | mA               |                            |

| Output Maximum Voltage    | VDSS    | 100     |              |          | V                | Vs=44V<br>IDSS=1mA         |

| FET On-State Resistance   | RDS(on) |         | 0.3          | 0.5      | Ω                | ID=1A                      |

| FET Diode Forward Voltage | VSD     |         | 0.8          | 1.1      | V                | IsD=1A                     |

| Maximum Clock Frequency   | Felock  |         |              | 100      | kHz              |                            |

| Logic Input Voltage       | VIL     |         |              | Vcc×0.25 | V                |                            |

| Logic Input Voltage       | VIH     | V∞×0.75 |              |          | V                |                            |

| Logic Input Current       | IIL     |         | ±1           |          | $\mu A$          |                            |

| Toge input current        | IIH     |         | ±1           |          | $\mu A$          |                            |

| REF Input Voltage         | VREF    | 0       |              | 1.5      | V                | Stationary current control |

| Input totage              | VREFS   | 2.0     |              | Vœ       | V                | Output OFF(Sleep)          |

| REF Input Current         | IREF    |         | ±10          |          | $\mu \mathbf{A}$ |                            |

| Sense Voltage             | VRs     |         | $V_{ m REF}$ |          | V                |                            |

October 2005

Electrical Characteristic (Ta=25°C,Vs=24V,Vcc=5V Unless Otherwise Noted)

| Characteristic           | Crashal  | Limits |     |     | T Took       | That Care dition                         |

|--------------------------|----------|--------|-----|-----|--------------|------------------------------------------|

| Characteristic           | Symbol   | MIN    | TYP | MAX | Unit         | Test Condition                           |

| PWM OFF Time             | TOFF     |        | 12  |     | $\mu { m S}$ |                                          |

| PWM Minimum ON Time      | TON(min) |        | 5   |     | $\mu S$      |                                          |

| Sleep-Enable return time | TSE      | 100    |     |     | $\mu S$      | VREF : 2.0→1.5 <sup>V</sup><br>Io : 1.5A |

| Switching Time           | TONC     |        | 2.5 |     | $\mu S$      | Clock→Out                                |

|                          | TOFFC    |        | 2.0 |     | $\mu S$      | Clock→Out                                |

### Truth table

| Pin Function | Low level           | High level            |

|--------------|---------------------|-----------------------|

| CW/CCW       | Forward(CW)         | Reverse(CCW)          |

| Full/Half    | Full Step           | Half Step             |

| REF          | Enable              | Output disable(Sleep) |

| Sync         | Non synchronous PWM | Synchronous PWM       |

| Clock        | Positive Edge       |                       |

October 2005

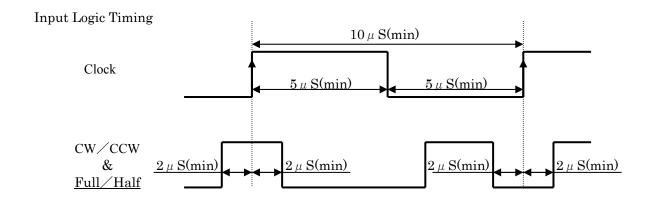

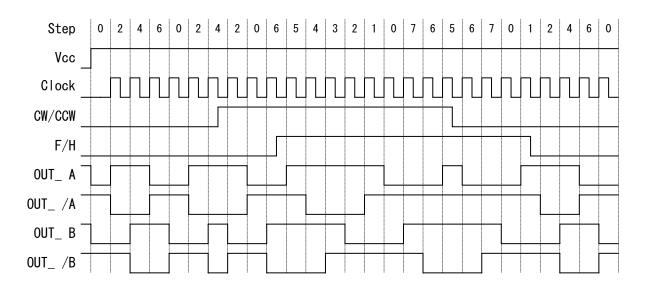

Timing chart

- This timing chart is a voltage mark.

- PWM signal for current control is not superimposed on this timing chart.

October 2005

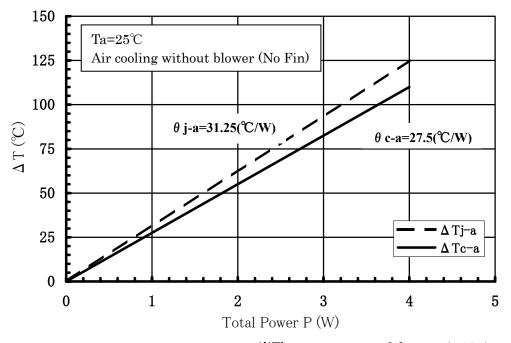

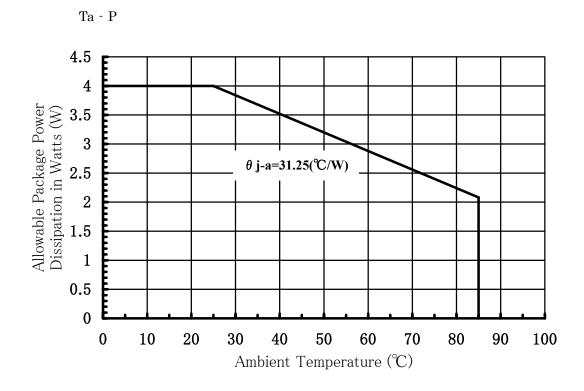

Heat design data

Total Power –  $\Delta$  T indegc

October 2005

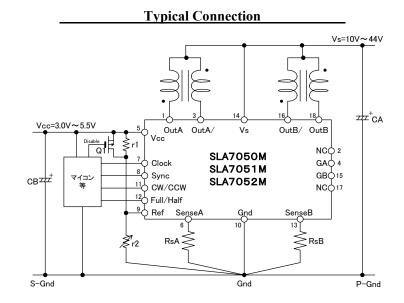

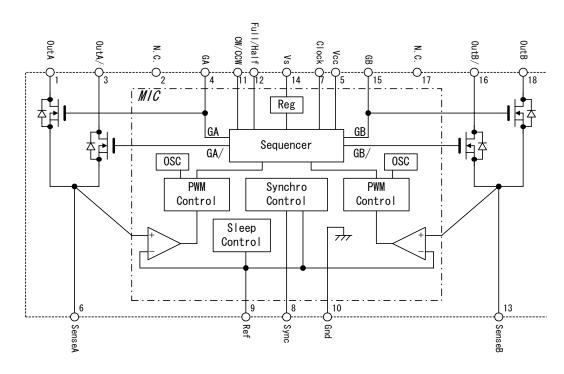

### **Block diagram (Connection diagram)**

### Pin arrangement, Functional table

| Pin Number | Symbol    | Function                           |

|------------|-----------|------------------------------------|

| 1          | OutA      | Phase A Output                     |

| 2          | N.C.      | No Contact                         |

| 3          | OutA/     | Phase A/ Output                    |

| 4          | GA**      | Phase A Gate                       |

| 5          | Vcc       | Logic supply                       |

| 6          | SenseA    | Phase A current sense              |

| 7          | Clock     | Step clock                         |

| 8          | Sync      | Synchronous PWM control            |

| 9          | Ref       | Current reference & Output disable |

| 10         | GND       | GND                                |

| 11         | CW/CCW    | Forward reverse control            |

| 12         | Full/Half | Full step half step control        |

| 13         | SenseB    | Phase B current sense              |

| 14         | Vs        | Load supply                        |

| 15         | GB**      | Phase B Gate                       |

| 16         | OutB/     | Phase B/ Output                    |

| 17         | N.C.      | No Contact                         |

| 18         | OutB      | Phase B Output                     |

%The gating signal of MOS FET outputs, and use 4pin and 15pin by the unwiring, please.

October 2005

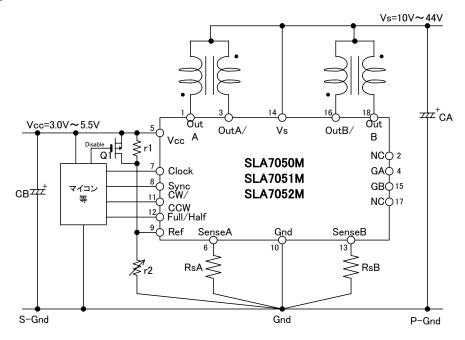

### **Example application circuit**

Reference constant  $Rs=0.1\sim 2\Omega (Loss \ attention \ P=Io^2\times Rs)$

$FIo^2 \times Rs$ ) CA=100  $\mu$  F/50V

$R1=10k\Omega$

CB=10 μ F/10V Q1:

$R2=5.1k\Omega(VR)$

☆Be careful of especially the noise on Vcc line.

If the noise on Vcc line exceeds 0.5V, a product may incorrect-operate.

- ☆When you do not use Logic inputs (CW/CCW and F/H, Sync), please be sure to connect with Vcc or GND.

- ☆To minimize the effect of system ground I·R drops on the logic and reference input signals, Ground pin should have a low-impedance return to system groud.

- ☆2pin,4pin,15pin and 17pin are No Contact.

October 2005

### Package information s

Package type and physical dimensions

#### Appearance

The body shall be clean and shall not bear any stain, rust or flaw.

### Marking

The type number and lot number shall be clearly marked in white.

October 2005

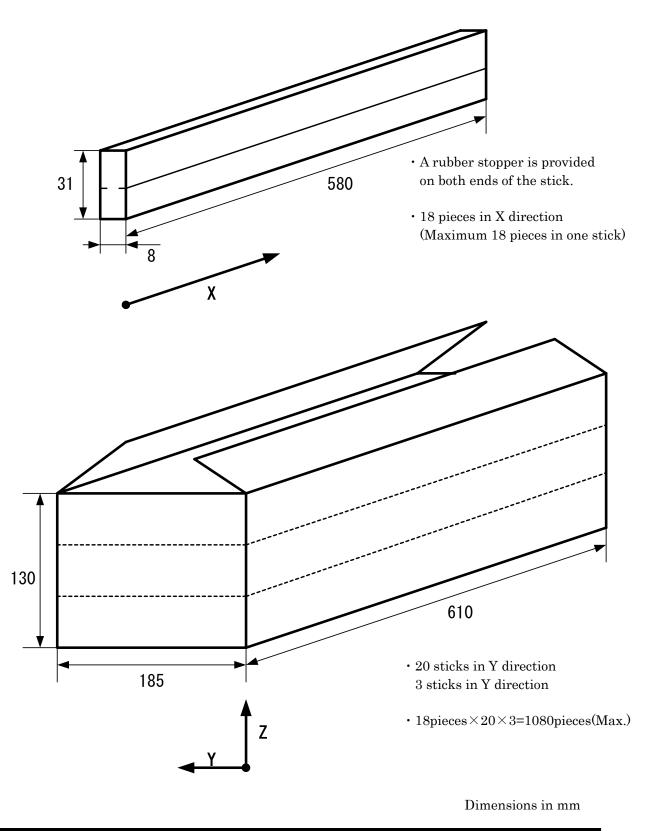

Packing specifications

Sanken Electric Co.,Ltd.

October 2005

### **Cautions and warnings**

The calculation of control current

SLA705xM Series control current Io is calculated as follow.

Io=VREF/Rs

REF Voltage range is 0.1V~1.0V

\*When the REF<0.1V, the accuracy of control current is reduce.

Moreover, if REF voltage is set up more than 2.0V, all outputs will be in OFF state.

#### Installation to a heat sink

1)Recommended Clamping Torque (to External Heat sink) 0.490~0.822N·m

2)Recommended Silicone

G746 {SHIN-ETSU CHEMICAL} YG6260 {GE TOSHIBA SILICONES}

SC102 {DOW CORNING TORAY SILICONE}

#### Notice

This driver has C-MOS inputs. Please notice as following contents.

- When static electricity is a problem, care should be taken to properly control the room humidity. This is particularly true in the winter when static electricity is most troublesome.

- Care should be taken with device leads and with assembly sequencing to avoid applying static charges to IC leads. PC board pins should be shorted together to keep them at the same potential to avoid this kind of trouble.