ÈęĐÇ”çŚÓĐûČŒ2027ÄêÁżČú1.4ÄÉĂŚĐŸÆŹ

ș«ÁȘÉçŸÉœđÉœ10ÔÂ3ÈՔ磏ÈęĐÇ”çŚÓ3ÈŐĐûČŒÓÚ2027ÄêÁżČú1.4ÄÉĂŚč€ÒŐ”ÄĐŸÆŹĄŁ

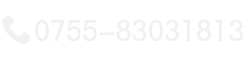

ÈęĐÇ”çŚÓ”±ÌìÔÚĂÀčúŒÓÖĘčèčÈŸÙ°ìĄ°ÈęĐÇŸ§ÔČŽúč€ÂÛÌł&SAFEÂÛÌłĄ±Čąč«ČŒșžÇÉÏÊöÄÚÈĘ”ÄŸ§ÔČÒ”Îń·ÏßÍŒșÍĐÂŒŒÊőĄŁÔÚʱžôÈęÄêÏßÏŸÙĐĐ”ÄŐ⳥ÂÛÌłÉÏŁŹÈęĐÇÊŚŽÎč«ČŒ1.4ÄÉĂŚĐŸÆŹÁżČúŒÆ»źĄŁÈęĐÇÓëĐĐÒ”ÁìÍ·ŃòÌš»ę”ç”ÄÄÉĂŚÖÆłÌŸșŐùœ«œűÒ»ČœŒÓŸçĄŁÌš»ę”ç”Ä3ÄÉĂŚÖÆłÌÒŃŸÍ¶ÈëÁżČúŁŹČąÏÈșóŚĆÊÖŃĐ·ą2ÄÉĂŚĄą1.4ÄÉĂŚÖÆłÌĄŁ

ÈęĐÇ”çŚÓÖśčÜŸ§ÔČŽúč€Ò”Îń”ÄÉ糀ŽȚʱÈÙ±íÊŸŁŹœ«»ùÓÚÏÂÒ»ŽúŸ§ÌćčÜœáččÈ«»·ÈÆŐ€Œ«(GAA)ŒŒÊőČ»¶ÏŽŽĐÂč€ÒŐŁŹŒÆ»ź2025ÄêÒęœű2ÄÉĂŚĐŸÆŹÖÆÔìč€ÒŐŁŹ2027ÄêÒęœű1.4ÄÉĂŚč€ÒŐĄŁÈęĐÇœńÄê6ÔÂÂÊÏÈÊ”ÏÖ3ÄÉĂŚÖÆłÌÁżČúŁŹŽËÇ°ÒŃÌáłö2ÄÉĂŚÖÆłÌÁżČúŒÆ»źĄŁ

ÁíÍ⣏ÈęĐÇ”çŚÓ»čÌáłö”œ2027ÄꜫłęÊÖ»ú”ÈÒƶŻČúÆ·ÖźÍâ”ÄČúÆ·ÏúÊÛ·Ę¶îÌážßÖÁ50%ÒÔÉÏ”ÄÄż±êĄŁ

1nmĐŸÆŹÊÇÊČĂŽžĆÄËüÓжàÀśșŠŁż

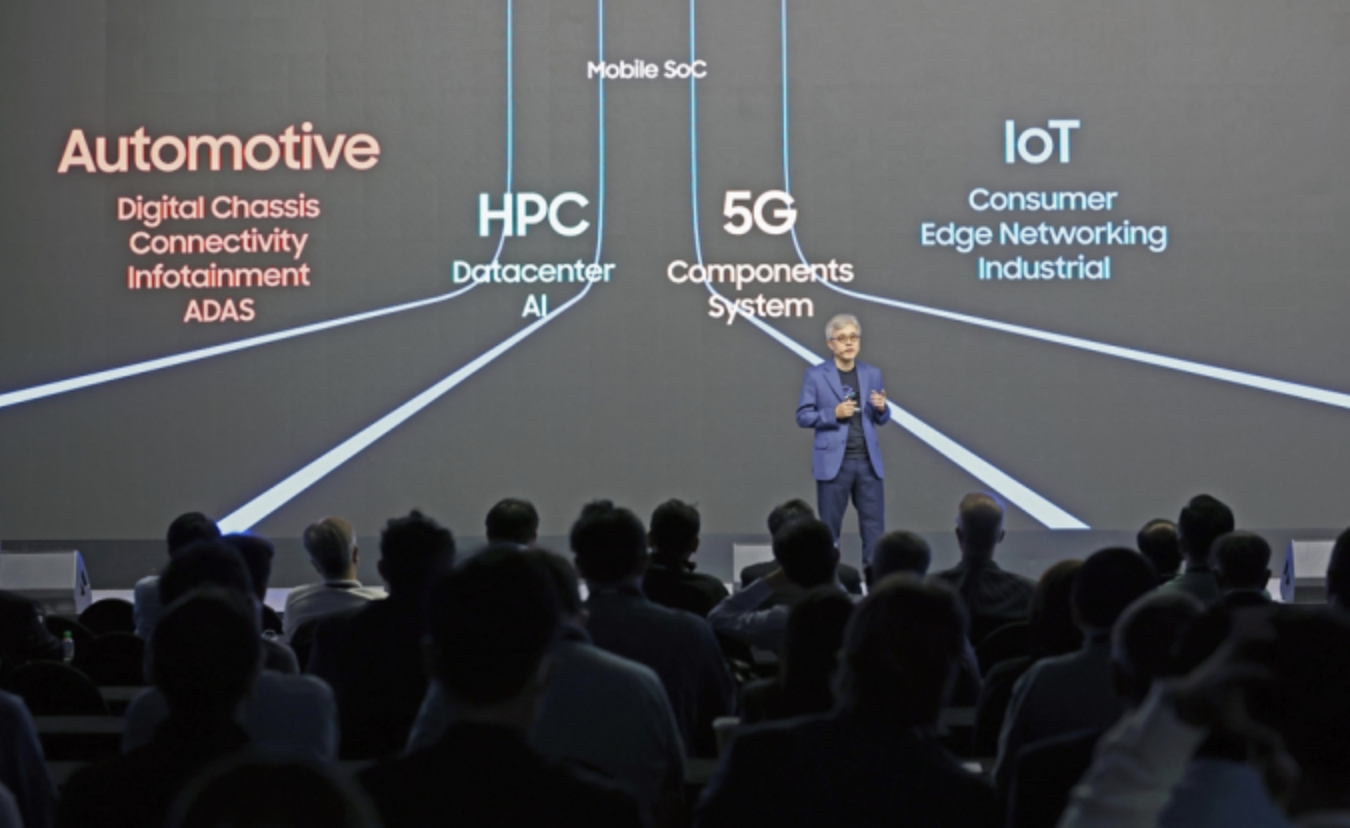

ŽÓĿǰ”ÄĐŸÆŹÖÆłÌŒŒÊőÉÏÀŽżŽŁŹ1nmŁšÄÉĂŚŁ©È·Ê”œ«œüŽï”œÁËŒ«ÏȚŁŹÎȘÊČĂŽŐâĂŽË”ÄŰŁżĐŸÆŹÊÇÒÔčèÎȘÖśÒȘČÄÁ϶űÖÆÔìłöÀŽ”ÄŁŹčèÔŚÓ”ÄÖ±Ÿ¶ÔŒ0.23ÄÉĂŚŁŹÔÙŒÓÉÏÔŚÓÓëÔŚÓÖźŒä»áÓĐŒä϶ŁŹĂżžöŸ§°û”ÄÖ±Ÿ¶ÔŒ0.54ÄÉĂŚŁšŸ§°ûÎȘččłÉŸ§Ìć”ÄŚî»ù±ŸŒžșΔ„ÔȘŁ©ŁĄ1ÄÉĂŚÖ»ÓĐÔŒ2žöŸ§°ûŽóĐĄĄŁ

1ÄÉĂŚ”„λ”œ”ŚÓжàĐĄŁż

ÄÉĂŚÒČÊôÓÚł€¶È”„λŁŹżÉÄÜșܶàÈËČ»ÁËœâËü”œ”ŚÓжàĐĄŁżșÁĂŚŁšmmŁ©ĄąÀćĂŚŁšcmŁ©ĄąĂŚŁšmŁ©ŽóŒÒ¶Œ±ÈœÏÊìÏ€ŁŹ10mm=1cmŁŹ100cm=1mŁŹ1mm=1/1000mĄŁ”„λł€¶ÈÓÉŽó”œĐĄĆĆÁĐÒÀŽÎÎȘŁșĂŚŁšmŁ©Ąą·ÖĂŚŁšdmŁ©ĄąÀćĂŚŁšcmŁ©ĄąșÁĂŚŁšmmŁ©ĄąÎąĂŚŁšŠÌmŁ©ĄąÄÉĂŚŁšnmŁ©ŁŹ1m=1000mmŁŹ1mm=1000ŠÌmŁŹ1ŠÌm=1000nmŁŹŒŽ1nm=10^-9mŁŹÏà”±ÓÚ1ĂŚÆœŸù·ÖłÉ10ÒÚ·ĘŁĄĂżÒ»·ĘÎȘ1nmĄŁ

ÓÉÓÚÄÉĂŚ”ÄÌŰÊâĐÔŁŹÒČŃʱäłöÁËÄÉĂŚŒŒÊőŁŹĐŸÆŹŒŒÊőÒČÊôÓÚÄÉĂŚŒŒÊő”Ä·¶łëĄŁ

ÄÉĂŚŒŒÊőÒČłÆșÀιÌŒŒÊőŁŹÊÇŃĐŸżłßŽçÔÚ1ÄÉĂŚÖÁ100ÄÉĂŚ·¶Î§ÄÚ”ÄČÄÁÏÓŠÓĂŒŒÊőŁŹ¶űŐâžöłßŽç·¶Î§»ù±ŸÊÇÔŚÓĄą·ÖŚÓĄąłŹ·ÖŚÓŒ¶±đ”ÄŁŹÒòŽËÓÖ±»łÆÎȘ·ÖŚÓÄÉĂŚŒŒÊőĄŁ

ÄÉĂŚŒŒÊőÖśÒȘ·ÖÎȘÈęŽóÀàŁș

ÄÉĂŚ»úÆśÈËŁŹ°Ń»úÆśÈËŚö”œÎąĐĄ»ŻŁŹŽï”œÄÉĂŚ”ÄŒ¶±đŁŹ»úÆśÈËżÉÒÔÈÎÒâŚéșÏ·ÖŚÓŁŹŸÍÏńŽî»ęÄŸÒ»ŃùĄŁŐâÖÖžĆÄî”ÄÄÉĂŚŒŒÊő»čÎŽÈĄ”ĂÖŰŽóœűŐ襣

ÄÉĂŚŒÓč€ŒŒÊőŁŹÖśÒȘÓŠÓĂÔڰ딌ÌćÖÆÔìÁìÓòŁŹŒŒÊőÒŃŸłÉÊìŁŹÄżÇ°ÒŃŸÁżČúÁË5nmč€ÒŐ”ÄĐŸÆŹŁŹ”äĐÍŽú±íÓĐŁșÌš»ę”猌Êő”ÄÆ»čûA14Ąąśèśë9000ŁŹÈęĐÇŒŒÊő”ÄæçÁú888ĄŁ

ÉúÎïÄÉĂŚŒŒÊőŁŹÊÇŽÓÉúÎïѧ”ÄœÇ¶Èłö·ą¶űÌáłö”ÄĄŁÔÚÏž°ûșÍÉúÎïÄ€ÄÚŸÍŽæÔÚÄÉĂŚŒ¶”Äœáč襣¶űŐâÖÖŒŒÊőŁŹżÉÒÔŽÙœűDNA·ÖŚÓŒÆËă»úĄąÏž°ûÉúÎïŒÆËă»ú”ÄżȘ·ąŁŹĐÎłÉÄÉĂŚÉúÎÊőĄŁ

ËæŚĆŒŒÊő”Ä·ąŐ裏ÄÉĂŚŒŒÊő”ÄÓŠÓĂ»áÔœÀŽÔœčă·șŁŹĐŸÆŹÖÆÔìč€ÒŐÒČ»áÔœÀŽÔœŸ«ÏžĄŁÄÉĂŚżÆѧŒŒÊőÒČ»áÒęÁìĐ”ĿÆѧŒŒÊőŁŹÈçŁșÄÉĂŚ»ŻŃ§ĄąÄÉĂŚ”çŚÓѧĄąÄÉĂŚÎïÀíѧĄąÄÉĂŚÉúÎïѧ”ÈĄŁ

ÖÆłÌŁšÄÉĂŚŁ©ÔÚĐŸÆŹÖĐŸżŸčÊÇÔőĂŽ»ŰÊÂŁż

ĐŸÆŹÓÖłÆŒŻłÉ”ç·ŁŹÊÇĂÀčúÏÉÍŻč«ËŸRobert NoyceÓë”ÂÖĘÒÇÆś»ù¶û±È·ąĂś”ÄŁŹŚîżȘÊŒ”ÄĐŸÆŹÊÇ°ŃŸ§ÌćčÜĄą”çŚèĄą”çŚè”ÈŒŻłÉÔÚÒ»žöșÜĐĄ”ÄÆœ°ćÉÏŁŹÈ»șóÓĂșÜÏž”ÄÏß°ŃŐâĐ©ÔȘÆśŒțÁŹœÓÆđÀŽŁŹÊ”ÏÖÁËŚîŒò”„”ÄĐŸÆŹčŠÄÜĄŁ

ËæŚĆĐŸÆŹŒŒÊőČ»¶Ï”Ű·ąŐ裏ÏÖÔÚ”ÄĐŸÆŹÒŃŸżÉÒÔŒŻłÉÉÏ°ÙÒڔğ§ÌćčÜŁŹÊ”ÏÖłŹŒ¶ŒÆËăčŠÄÜĄŁ¶űÖÆÔìč€ÒŐÒČŽï”œÁË5nmÖÆłÌĄŁ

șܶàÍűÓŃÈÏÎȘŐâžöč€ÒŐÖÆłÌ5nmÊÇŸ§ÌćčÜł€¶ÈŁŹÆäÊ”Čą·ÇÈçŽËĄŁÄÇĂŽŐâ5nmÖÆłÌŸżŸčÊÇÖž”ÄĐŸÆŹ”ÄÄÄžöȿλÄŰŁż

ÔÚŸ§ÌćčÜœáččÖĐŁŹ”çÁśŽÓSourceŁšÔŽŒ«Ł©ÁśÈëDrainŁšÂ©Œ¶Ł©ŁŹGateŁšŐ€Œ«Ł©Ïà”±ÓÚŐąĂĆŁŹÖśÒȘžșÔđżŰÖÆÁœ¶ËÔŽŒ«șÍ©Œ¶”ÄÍš¶ÏĄŁ¶űŐ€Œ«”ÄŚîĐĄżí¶ÈŁšŐ€ł€Ł©ŁŹŸÍÊÇŐâžöč€ÒŐÖÆłÌ5nmĄŁ

ÄÇĂŽÈçșÎČĆÄÜ°Ńžü¶à”ÄŸ§ÌćčÜ·Ć”œÓĐÏȚ”ÄĐŸÆŹÖĐÄŰŁż

ÄÇŸÍÊÇËőĐĄĐŸÆŹÖĐ”ÄŐ€Œ«ĄŁ¶űŐ€Œ«żí¶ÈÔœĐĄŁŹÒâζŚĆŐąĂĆÍš”ÀÔœĐĄŁŹÄÇĂŽ”„λĂæ»ęËùÈĘÄɔğ§ÌćčÜŸÍ»áÔœ¶àŁŹĐŸÆŹĐÔÄÜÒČŸÍÔœÇżŁŹĐŸÆŹÒČŸÍÔœÏÈœűĄŁ

ÎÒĂÇÒÔ5nmÎȘÀ꣏č€ÒŐÖÆłÌÖž”ÄÊÇĐŸÆŹŐ€Œ«żí¶ÈŁŹŐâžöżí¶ÈÊÇ5nmĄŁËőĐĄŸ§ÌćčÜ”ÄÄż”ÄÖśÒȘÓĐÁœ”ăŁșÒ»ÊÇŁŹŒőÉÙșÄ”çÁżŁŹŽÓ¶űŽï”œœ””ÍĐŸÆŹÄÜșÄ”ÄÄż”ÄŁ»¶țÊÇŁŹÔöŒÓŸ§ÌćčÜÊęÁżŁŹŽÓ¶űŽï”œÔöÇżĐŸÆŹĐÔÄÜ”ÄÄż”ÄĄŁ

ÄÇĂŽÒȘËőĐĄĐŸÆŹÄÄÒ»Čż·ÖŁŹČĆÄ܎ŐâŃù”ÄЧčûÄŰŁżŽđ°žÈÔÈ»ÊÇŐ€Œ«ĄŁ

Ő€Œ«Łș”±Ÿ§ÌćčÜ而śÊ±șòŁŹ”çÁśŽÓ©Œ«ÁśÏòÔŽŒ«ŁŹ”«ÊÇÊÜ”œÒ»”À·§ĂƔĿŰÖÆŁŹŐâ”ÀŐąĂĆŸÍÊÇŐ€Œ«ĄŁ¶űÎÒĂÇłŁË””Ä7nmĄą5nmŸÍÊÇŐâ”ÀŐąĂƔĿí¶ÈŁŹÒČŸÍÊÇŐ€Œ«”Äżí¶ÈĄŁÍščęËőĐĄŐ€Œ«żí¶ÈŁŹŽÓ¶űŽï”œœ””ÍĐŸÆŹÄÜșÄĄąÔöÇżĐŸÆŹĐÔÄÜĄŁ

ÒòŽËŁŹÎÒĂÇłŁË””Ä7nmĄą5nmÖž”ÄȹȻÊÇŸ§Ìćčܔij€¶ÈĄążí¶ÈŁŹ¶űÊÇË””ÄŐ€Œ«żí¶ÈĄŁ

ĐŸÆŹÖÆÔìÉÌÎȘÁËÉęŒ¶ĐŸÆŹĐÔÄÜŁŹÒČŸÍ°ŃŐ€Œ«żí¶ÈŚö”ÄÔœŐŁŹÒČŸÍÊÇÄÉĂŚŒ¶±đÔœĐĄŁŹĐŸÆŹĐÔÄÜÔœÏÈœűĄŁ

ÄÉĂŚÔœĐĄŁŹĐŸÆŹÔœÏÈœűÂđ?

ÄÉĂŚÔœĐĄŁŹĐŸÆŹÔœÏÈœűÂ𣿔ÄÈ·ÊÇ

ÊŚÏÈÎÒĂÇŽÓÀíÂÛÉÏÀŽ·ÖÎöŁș

ËőĐĄč€ÒŐÖÆłÌÓĐÄÄĐ©șĂŽŠÄŰŁż

1Ąąœ””ÍÄÜșÄ

ËőĐĄč€ÒŐÖÆłÌșóŁŹŸ§ÌćčÜÖźŒä”ÄÍš”À±äŐŁŹŸ§ÌćčÜÖźŒä”Ä”çÈĘÒČ»á±ä”ÍŁŹŽÓ¶űÌáÉężȘčŰ”ÄÆ”ÂÊĄŁ¶űŸ§ÌćčÜżȘčŰÏûșĔĔçÁżÓë”çÈĘłÉŐę±ÈŁŹÒòŽËŁŹ”çÈĘœ””ÍșóŁŹżȘčŰËٶȞüżìĄąÒČžüÊĄ”祣

ŽËÍ⣏č€ÒŐžüŸ«Ïž”ÄĐŸÆŹŁŹĐèÒȘžü”͔ĿȘčŰ”çŃ裏ÒČÄÜœ””ÍČż·ÖÄÜșÄĄŁ

2ĄąœÚÔŒČÄÁÏ

ĐŸÆŹÏòŚĆžüĐĄ”Äč€Òճߎçœű·ąŁŹ»á”ŒÖÂŚéŒțžüĐĄŁŹÒ»ÆŹŸ§ÔČÇĐžîłöÀŽ”ÄĐŸÆŹŸÍ»ážü¶àŁŹœű¶űœÚÔŒČÄÁÏŁŹŽï”œœ””ͳɱŸ”ÄÄż”ÄĄŁ

”«ÊÇŁŹ”±ĐŸÆŹč€ÒŐŽï”œÒ»¶šłÌ¶ÈșóŁŹÓÈÆäÊÇœűÈë7nmč€ÒŐșóŁŹžß°ș”ÄÉ豞łÉ±ŸĄąŸ«Ïž»ŻÖÆÔìĄąÎȚłŸ»Żč€ł§”È·Ž¶űÍÌÊÉÁËŸ§ÔČÇĐžîłöÀŽ”Äžü¶àŸ§ÆŹĄŁ

3ĄąÂúŚăÇᱥÉ豞”ÄĐèÇó

ËőĐĄč€Òճߎç»čÓĐÒ»žöșĂŽŠŁŹŸÍÊÇżÉÒÔÔÚČ»±äŽóĐŸÆŹ”ijߎçÇ°ÌáÏÂŁŹÌážßĐŸÆŹÄÜĐÔÄÜŁŹÒԎÌážßÊÖ»úĄą”çÄÔĐÔÄÜ”ÄÄż”ÄĄŁ

ÍŹÊ±žßĐÔÄÜŁŹĐĄłßŽç”ÄĐŸÆŹÒČÓĐÖúÓÚÖÆÔìÇᱥÉ豞ŁŹÊčÉ豞ÏòÇᱥĐÍĄąÎąĐĄĐÍœűŸüĄŁ

ÎÒĂÇÔÙÓĂÊ”ÀęÀŽ¶Ô±ÈŁș

1Ąąśèśë970ČÉÓĂÌš»ę”ç10nmč€ÒŐÖÆłÌŁŹșËĐÄÊęÁż12ŁŹÓĐ55ÒÚŸ§ÌćčÜĄŁ

CPUŁș8șËCPUŁŹ4žö2.4GHz Cortex-A73șËĐÄ+4žö1.8GHz Cortex-A53șËĐÄŁ»

GPUŁș12șËŁŹMali-G72ŒÜč裻

2Ąąśèśë990ČÉÓĂÌš»ę”ç7nmč€ÒŐÖÆłÌŁŹșËĐÄÊęÁż16ŁŹÓĐ103ÒÚŸ§ÌćčÜŁŹŸ§ÌćčÜÊęÁżÔöŒÓ48ÒÚžöŁŹÔŒ87%ŁŹœÏÉÏÒ»ŽúĐŸÆŹĐÔÄÜÌáÉę33%ŁŹÄÜșÄœ””Í50%ĄŁ

CPUŁș8șËCPUŁŹ2žö2.86GHz Cortex-A76șËĐÄ+2žö2.36GHz Cortex-A76șËĐÄ+4žö1.95GHz Cortex-A55șËĐÄŁ»

GPUŁș12șËŁŹMali-G76ŒÜč裻

NPUŁș:ŚÔŃДĎï·ÒÆæŒÜččNPUŁŹË«ŽóșË NPU +ÎąșË NPUĄŁ

3Ąąśèśë9000ČÉÓĂÌš»ę”ç5nmč€ÒŐÖÆłÌŁŹÓĐ194ÒÚŸ§ÌćčÜŁŹŸ§ÌćčÜÊęÁżÔöŒÓ91ÒÚžöŁŹÔŒ88%ŁŹœÏÉÏÒ»ŽúĐŸÆŹĐÔÄÜÌáÉę50%,čŠșÄœ””Í30%ĄŁ

CPUŁș8șËCPUŁŹ2žö3.13GHz Cortex-A76șËĐÄ+2žö2.54GHz Cortex-A76șËĐÄ+4žö2.05GHz Cortex-A55șËĐÄŁ»

GPUŁș24șËŁŹMali-G76ŒÜč裻

NPUŁș:Ë«ŽóșË NPU +ÎąșË NPUĄŁ

Íščę¶Ô±ÈŁŹÎÒĂÇżÉÒÔżŽłöč€ÒŐÖÆłÌÔœĐĄŁŹĐŸÆŹÔœÏÈœűĄŁŸ§ÌćčÜÊęÁżžü¶àĄąCPUĐÔÄÜžüžßĄąșËĐÄÊęÒČÔœ¶àĄąŚîÖŐÌážßÁËĐŸÆŹ”ÄŐûÌćĐÔÄÜĄŁ

ĐŸÆŹÖÆłÌÔœĐĄÔœÏÈœűŁŹÄÇĂŽĐŸÆŹÖÆłÌ”ÄŒ«ÏȚÊǶàÉÙÄÉĂŚŁż

ÊŚÏÈÀŽÁËœâÒ»ÏÂÄŠ¶û¶šÂÉ

ÄŠ¶û¶šÂÉŁșÓÉÓąÌ۶ûŽŽÊŒÈËÖźÒ»žê”ÇÄŠ¶ûÌáłöŁŹÖž”ÄÊÇ”±ŒÛžńČ»±äʱŁŹŒŻłÉ”ç·ÉÏżÉÈĘÄÉ”ÄÔȘÆśŒț”ÄÊęÄżŁŹÔŒĂżžô18-24žöÔ±ă»áÔöŒÓÒ»±¶ŁŹĐÔÄÜÒČœ«ÌáÉęÒ»±¶ĄŁŐâÒ»¶šÂÉœÒÊŸÁËĐĆÏąŒŒÊőœűČœ”ÄËÙ¶ÈĄŁ

ÄŠ¶û¶šÂɶÔĐŸÆŹÖÆÔìÒ”Ó°ÏìÉîÔ¶ŁŹÔÚŒžÊźÄê”Ä·ąŐččęłÌÖĐŁŹĐŸÆŹżȘ·ąÉÌÒ»Ö±°ŽŐŐŐâžö¶šÂÉÔÚÖđČœ”üŽúĐŸÆŹŁŹŽÓ10ιÌ”œ1ιÌŁŹÔÙ”œ90ÄÉĂŚŁŹËæșóœűÈë65ÄÉĂŚĄą45ÄÉĂŚĄą32ÄÉĂŚŁŹ”œÏÖÔÚ”ÄÁżČú5nmĄŁĐŸÆŹČ»¶Ï”Ű”üŽúŁŹÄÇĂŽŸżŸč¶àÉÙÄÉĂŚŁŹČĆÊÇĐŸÆŹÖÆłÌ”ÄŒ«ÏȚŁŹČĆÊÇĐŸÆŹÖÆÔì”ÄÌìżŐÄŰŁż

ÔűŸÒ»¶ÈÈÏÎȘ7nmÊÇĐŸÆŹ”ÄÎïÀ팫ÏȚ

7nmÖźËùÒÔ±»ÈÏÎȘÊÇĐŸÆŹÎïÀ팫ÏȚŁŹÊÇÒòÎȘŁŹ”±ÖÆłÌ”ÍÓÚ7nmʱŁŹŸ§ÌćčÜ·ÇłŁŒŻÖĐŁŹ¶űÇÒŸàÀë·ÇłŁœüŁŹŐ€Œ«”Äșń¶ÈÒČœÓœüŒ«ÏȚŁŹÒòŽËÈĘÒŚČúÉúÁżŚÓË펩ЧӊŁŹÂ©”çÂÊ»áŽó·ùÔöŒÓŁŹÈçčûÎȚ·šżŰÖÆ©”çÂÊŁŹÄÇĂŽÖÆÔìč€ÒŐœ«ÖčČœÓÚŽËĄŁ

ĐŸÆŹÖÆÔìčęłÌÖĐŁŹčâżÌ»úËù·ąłö”ÄŒ«ŚÏÍâčâ»áŽæÔÚŃÜÉäÏÖÏóŁŹ”ŒÖÂčâżÌŐ€ł€ČąČ»Êź·ÖŸùÔÈŁŹÍŹÊ±ŁŹÔÚÖÆÔìčęłÌÖĐŁŹÀëŚÓŚąÈëĄąÊŽżÌĄą”ÈÀëŚÓłćÏŽĄąÈÈŽŠÀí”ÈČœÖèŁŹÒČ»á”ŒÖÂÊ”ŒÊŐ€ł€Č»ŸùÔÈĄŁ

ÒòŽËŁŹÓÉÓÚŐ€ł€Č»ŸùÔÈ”ÄÎÊÌ⣏ŸÍ”ŒÖÂĐĐÒ”ÆŐ±éÈÏÎȘ7nmč€ÒŐŸÍÊÇĐŸÆŹ”ÄÎïÀ팫ÏȚĄŁ

7nmĄą5nmŒŒÊőÖđœ„č„ÆÆ

2019Äê8ÔÂŁŹÈęĐÇ·ąČŒÆìœąĐŸÆŹExynos 9825ŁŹ±êÖŸŚĆ7nmEUVŒŒÊő”ÄłÉ芥ŁÒ»žöÔÂșóŁŹÆ»čû·ąČŒĐ»úĐÍŁŹŽîÔŰ”ÄĐŸÆŹČÉÓĂÁËÌš»ę”ç7nm EUVŒŒÊőĄŁ

2020Äê10ÔÂŁŹÆ»čû·ąČŒiPhone 12ŽîÔŰÁËA14ŽŠÀíÆśŁŹ»ȘÎȘ·ąČŒÁËMate40ŽîÔŰÁËśèśë9000ŽŠÀíÆśĄŁŐâÁœżîŽŠÀíÆśŸùČÉÓĂÁË5nm EUVŒŒÊőĄŁ

ÒČŸÍÊÇŽ«Íł”ÄčèČÄÁÏŁŹÄÜč»ÁżČú7nmĄą5nmÖÆłÌ”ÄĐŸÆŹĄŁ

žśŽół§ÉÌżȘÊŒœűŸü3nmĄą2nmč€ÒŐ

2020Äê8ÔÂ25ÈŐżȘÄ»”ÄÔÚÌš»ę”ç”Ú26œìŒŒÊőŃĐÌÖ»áÉÏŁŹÌš»ę”çč«ČŒÁËžüÏÈœű”Ä3nmĄą4nmč€ÒŐŁŹŽËÍâŁŹÌš»ę”ç»čŐęÊœĐûČŒœšÉèĐ”ÄŃĐ·ąÖĐĐÄŁŹÔ€ŒÆœ«Í¶Èë8000¶àĂû耳ÌÊŠ”ÄÈËÁŠ”œÒ»ÌőÏÈœűč€ÒŐÉúČúÏßÉÏŁŹŚĆÁŠč„żË2nmč€ÒŐĄŁ

ÈęĐÇÒČĐûČŒÁË3nm”ÄĐŸÆŹŁŹČÉÓĂGAAFETŸ§ÌćčÜŒŒÊőŁŹĐŸÆŹÁśÆŹłÉ芣ŹœÓÏÂÀŽŐæŐęœűÈëÁżČúœŚ¶ÎÁËŁŹČ»ÔÙÊÇPPTŁŹ¶űÊÇʔʔÔÚÔÚ”ÄĐŸÆŹŒŒÊőÁËĄŁ

¶űŚîœüÌš»ę”çÓÖÓëÌšŽóĄąÂéÊĄÀíč€șÏŚśŁŹŃĐŸżÓöțÎŹČÄÁÏœáșÏŁŹŽï”œŒ«”Í”çŚèŁŹœÓœüÁżŚÓŒ«ÏȚŁŹŚîÖŐÌôŐœ1nmč€ÒŐÖÆłÌĄŁ

żÉÒÔżŽłöŁŹÌš»ę”祹ÈęĐÇŐâĐ©Žół§ŁŹÍščęžÄÁŒŒŒÊőŁŹČÉÓĂĐÂČÄÁÏŁŹčÀŒÆŚîÖŐ°Ńčè»ùČÄÁÏ”ÄĐŸÆŹ”Äč€ÒŐŚö”œ1nmĄŁ

Ö»ÓĐČÉÓĂĐÂČÄÁÏČĆÄÜÍ»ÆÆÄŠ¶û¶šÂÉ

șܶàʱșòŁŹŒŒÊő”ÄÍ»ÆƶŒÊÇÓÉČÄÁÏ”ÄÍ»ÆÆżȘÊŒ”ÄĄŁžÖÌú”Ä”źÉúŁŹŽÙœűÁËÈËÀàč€Ò””ÄżìËÙ·ąŐ裻É黯ïŰŁšGaAsŁ©”Ä”źÉúŁŹŒ«Žó”ÄŽÙœűÁËLEDÆÁ”Ä·ąŐ裻ÌᎿčè”Ä”źÉúŁŹŒ«Žó”ÄŽÙœűÁËĐŸÆŹŒŒÊő”Ä·ąŐ襣

¶űÍŹŃùŁŹĐŸÆŹč€ÒŐÔÙÍ»ÆÆŁŹĐèÒȘœűĐĐÒ»łĄČÄÁÏžïĂüĄŁœèÖúĐÂČÄÁÏŒŒÊőŁŹÍ»ÆÆÄŠ¶û¶šÂÉÊÇÎŽÀŽżÉĐДķœ·šĄŁ¶űÇÒŁŹČż·ÖŽół§șÍŃĐŸż»úččÒŃŸżȘÊŒŃĐŸżÁËŁŹČąÇÒÈĄ”ĂÁËČż·ÖœűŐ襣

ÖĐčúÁìÏÈÌŒÄÉĂŚčÜŒŒÊő

2017Äê±±Ÿ©Žóѧ”çŚÓÏ”œÌÊÚŒæÖĐżÆÔșÔșÊżĆíÁ·ĂŹÍƶӳÉÁËÌŒÄÉĂŚčÜŁŹÊŚŽÎÔÚÊ”ŃéÉÏÏÔÊŸłöÌŒÄÉĂŚčÜÆśŒțșÍŒŻłÉ”緜ώ«ÍłŒŒÊő”ÄĐÔÄÜÓĆÊÆŁŹ2020Äê5ÔÂÌŒ»ùĐŸÆŹŃĐŸżč€ŚśÈĄ”ĂÖŰŽóœűŐ裏ȹÔÚčúŒÊ¶„Œ¶żÆѧÆÚżŻĄ¶żÆѧĄ·ÉÏ·ą±íÁËłÉčûĄŁ

ÌŒÄÉĂŚčÜŸßÓĐ¶à·œĂæÓĆÊÆŁș

ŚÛșÏĐÔÄÜ10±¶ÁìÏÈÓÚÍŹÊ±ÆÚĐÔÄÜŚîÓĆ”Äčè»ùŸ§ÌćčÜŁ»Æä而śËÙ¶È3±¶ÓÚÓąÌ۶ûŚîÏÈœű”Ä14nmÉÌÓĂčèČÄÁÏŸ§ÌćčÜŁŹÄÜșÄÖ»ÓĐč蟧ÌćčÜËÄ·ÖÖźÒ»ĄŁ

ÌŒÄÉĂŚčܔijɱŸ”ÍŁŹ¶űÇÒłßŽçĐĄŁŹÖ»ÓĐ1-3nmŁŹžüÊÊșÏŚöĐĄłßŽçĐŸÆŹŁŹÇÒÇż¶ÈžßÓÚžÖÌúŁŹČąŸßÓĐ”ŻĐÔŁŹżÉÒÔŚöŐÛ”țĐŸÆŹŁŹÒČżÉÒÔÖÆŚśÍžĂśĐŸÆŹ”ÈĄŁ

ÌŒ»ùĐŸÆŹÒČÓĐËü”ÄČ»ŚăÖźŽŠŁș

ÊŚÏÈÖÆŚśč€ÒŐÂäșóčè»ùĐŸÆŹŁŹÖÆłÌÉÏԶȻÈçčè»ùĐŸÆŹŁŹÖÆŚśč€ÒŐÄŃ¶ÈžüŽóŁŹÌŒÄÉĂŚčÜĐèÒȘÌᎿ”œ99.9999%ČĆżÉÒÔÖÆŚśĐŸÆŹŁŹ¶űĿǰÊÔŒÁč«ËŸÖ»ÄÜÌᎿ”œ99.99%ĄŁ

łęÁËÌŒÄÉĂŚčÜÍ⣏”Ș»ŻïŰșÍÌŒ»ŻčèĄą¶țÁò»Żî⥹čèÏ©Òȱ»łÆÎȘÏÂÒ»ŽúĐŸÆŹČÄÁÏĄŁ

GaNĄąSiCŁš”Ș»ŻïŰșÍÌŒ»ŻčèŁ©ŁŹŐâÁœÖÖĐÂĐÍČÄÁÏÒŃŸÔÚĐŸÆŹÁìÓòżȘʌӊÓĂÁËŁŹČąÇÒŸßÓĐżíœûŽűĄąžßÈÈ”ŒÂÊĄąžß»śŽ©”糥Ąąžßżč·űÉäÄÜÁŠ”ÈÌ۔㣻

¶țÁò»Żî⣚MoS2Ł©ŁŹ¶țÁò»ŻîâÒŃŸÔÚÊ”ŃéÊÒÖĐ”źÉúÁËŁŹ¶űÇÒ1ÄÉĂŚč€ÒŐÖÆłÌÖбíÏÖȻˌŁ»

čèÏ©ŁŹčèșÍÌŒŸßÓĐÏàËƔĻŻŃ§ĐÔÖÊŁŹŃĐŸżÈËÔ±ÍÆČâčèÔŚÓÒČżÉÒÔÏńÊŻÄ«Ï©ÄÇŃùŁŹÔŚÓłÊ·äÎŃŚŽĆĆÁĐŁŹĐÎłÉčèÏ©ŐâÖÖÎïÖÊĄŁÓëÊŻÄ«Ï©”ÄÖŰÒȘȻ͏ÔÚÓÚŁŹčèÏ©Ó”ÓĐżÉÒÔÊ”ÏÖÂߌ”ç·Ëù±ŰÒȘ”ÄÄÜ϶ŁŹ”«ÊÇčèÏ©ŚîŽó”Äȱ”ăŸÍÊÇČ»ÎȶšŁŹ¶űÇÒ±ŁŽæʱŒäÒČ¶ÌĄŁ

ÎŽÀŽĐŸÆŹÄÜ·ńÍ»ÆÆ1nmč€ÒŐÖÆłÌŁŹœűÈëÈ«ĐÂÈü”ÀŁŹ±ŰĐëÒÀżżĐÂČÄÁÏŒŒÊőŁŹÈçŁșÌŒÄÉĂŚčÜĄą”Ș»ŻïŰșÍÌŒ»ŻčèĄą¶țÁò»Żî⥹čèÏ©ĄŁ

ĐŸÆŹ”„λÄÉĂŚŁŹČą·ÇÊÇŸ§ÌćčÜł€¶ÈŁŹ¶űÊÇŸ§ÌćčÜÖĐ”ÄŐ€Œ«żí¶ÈĄŁ

ÎȚÂÛÊÇÀíÂÛÉÏŁŹ»čÊÇÊ”ŒÊÇéżöŁŹĐŸÆŹč€ÒŐÖÆłÌÔœĐĄŁŹĐŸÆŹÔœÏÈœűŁŹĐÔÄÜÔœșĂĄŁ

łŁÓĂ”Äčè»ùĐŸÆŹŒ«ÏȚč€ÒŐÖÆłÌÊÇ1nmĄȘ3nmŁŹÈçčûÒȘÍ»ÆÆŐâžöŒ«ÏȚŁŹŒŽ±ŰĐëÒȘČÉÓĂĐÂČÄÁÏŁŹÀęÈçŁșÌŒÄÉĂŚčÜĄą”Ș»ŻïŰșÍÌŒ»ŻčèĄą¶țÁò»Żî⥹čèÏ©ĄŁ

Ąű ŚąŁșÎÄŐÂŐûÀíŚȘÔŰÓÚÍűÂ磏œöč©ČÎżŒŃ§Ï°ŁŹ°æÈščéÔŚśŐßËùÓĐŁŹÈçÉ挰ÇÖÈšŁŹÇëÁȘÏ”ĐĄ±àÉŸłęĄŁ

PreŁșζȎ«žĐÆś”ÄÓŠÓĂłĄŸ° 2026-05-07

NextŁșĂÀčúÓûÏȚÖƶÔÖĐčúŽæŽąĐŸÆŹÉúČúÉ豞łöżÚŁŹÈęĐÇĄąșŁÁŠÊżŽ«Č»ÊÜŐțČßÏȚÖÆ 2026-05-07

Collect

Collect

NavigateŁș

NavigateŁș