«≥ћЄѕ»љшЈв„∞ЉЉ х£ђ ≤√і «ѕ»љшЈв„∞£њ

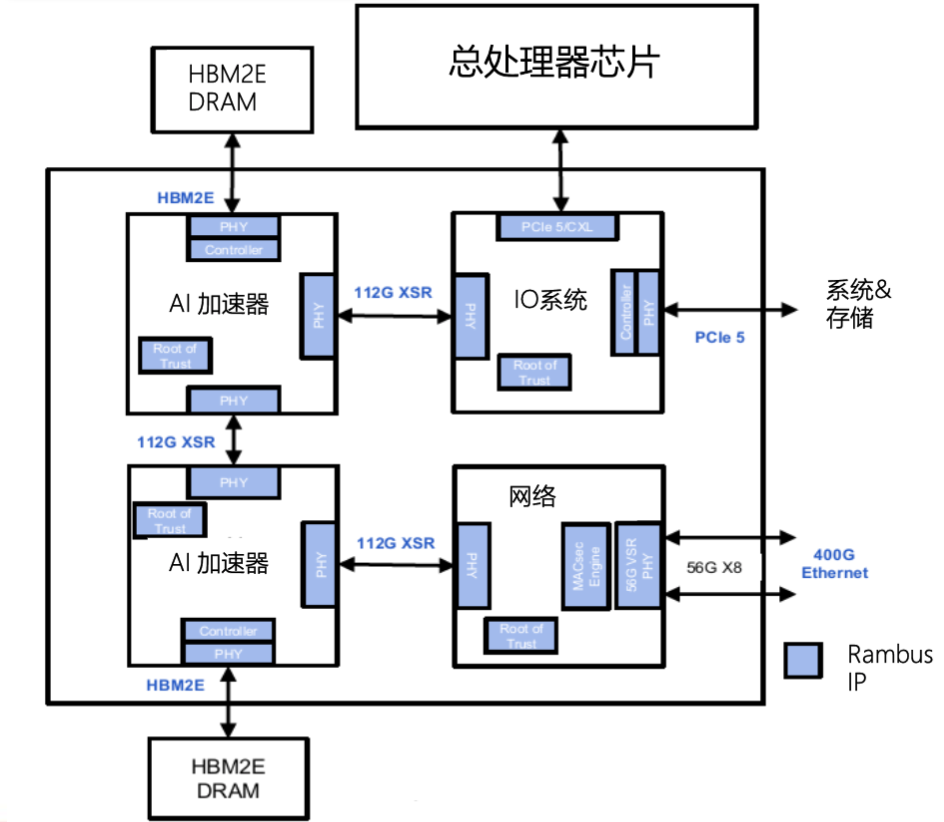

Јв„∞ «÷ЄљЂ…ъ≤ъЉ”є§ЇуµƒЊІ‘≤љш––«–Єо°ҐЇЄѕяЋ№Јв£ђ єµз¬Ј”лЌв≤њ∆чЉю µѕ÷Ѕђљ”£ђ≤Ґќ™∞лµЉће≤ъ∆Јћбє©їъ–µ±£ї§£ђ є∆д√в №ќпјн°Ґїѓ—Іµ»їЈЊ≥“тЋЎЋр Іµƒє§“’°£

Ћж„≈∞лµЉћеѕ»љш÷∆≥ћ≤їґѕЌщ7nm/5nm£ђ…х÷Ѕ“‘ѕ¬¬хљш£ђЊІ∆ђ…иЉ∆”л÷∆‘мє§“’ќҐЋхµƒƒ—ґ»°Ґ≥…±Њ”лњ™ЈҐ ±ЉдЊщ≥ ѕ÷ћш‘Њ љµƒ‘ц≥§°£

√жґ‘іЋƒ—ћв£ђЊІ∆ђ“µ’я ‘ЌЉЌЄєэѕ»љшЈв„∞јііпµљЊІ∆ђЉдµƒЄя√№ґ»ї•Ѕ™£ђ“‘ µѕ÷“‘ЄьµЌ≥…±Њћбє©Ќђµ»Љґ–Іƒ№±нѕ÷°£

ѕ»љшЈв„∞≤…”√ЅЋѕ»љшµƒ…иЉ∆ЋЉ¬ЈЇЌѕ»љшµƒЉѓ≥…є§“’£ђґ‘–Њ∆ђљш––Јв„∞Љґ÷Ўєє£ђ≤Ґ«“ƒ№”––Іћб…эѕµЌ≥Єяє¶ƒ№√№ґ»µƒЈв„∞ЉЉ х°£

ѕ»љшЈв„∞є§“’∞ьј®µє„∞ЇЄ(FlipChip)°ҐЊІ‘≤ЉґЈв„∞(WLP)°Ґ2.5DЈв„∞£®Interposer£© °Ґ3DЈв„∞ (TSV)°ҐChipletµ»°£

Ћж„≈∞лµЉће÷∆≥ћљЏµгµƒ≥÷–ш—Ёљш£ђґћєµµј–І”¶“‘Љ∞Ѕњ„”Ћні©–І”¶ішјіµƒЈҐ»»°Ґ¬©µзµ»ќ ћв”ъЈҐ—ѕ÷Ў£ђ„Ј«уЊ≠Љ√–Іƒ№µƒƒ¶ґыґ®¬…»’«чЈ≈їЇ°£

‘ЏіЋ±≥Њ∞ѕ¬£ђ≤ъ“µњ™ ЉЋЉњЉљЂ≤їЌђє§“’µƒƒ£њйїѓ–Њ∆ђ°£

Chiplet”÷≥∆–ЊЅ£їт–°–Њ∆ђ£ђ «ѕ»љшЈв„∞ЉЉ хµƒіъ±н£ђљЂЄі‘”–Њ∆ђ≤рљв≥…“ї„йЊя”–µ•ґјє¶ƒ№µƒ–°–Њ∆ђµ•‘™ die£®¬г∆ђ£©£ђЌ®єэ die-to-die љЂƒ£њй–Њ∆ђЇЌµ„≤гїщі°–Њ∆ђЈв„∞„йЇѕ‘Џ“ї∆р°£

Chiplet µѕ÷‘≠јн”ліоїэƒЊѕаЈ¬£ђі”…иЉ∆ ±ЊЌ∞і’’≤їЌђµƒЉ∆Ћгµ•‘™їтє¶ƒ№µ•‘™ґ‘∆дљш––Ј÷љв£ђ»їЇу√њЄцµ•‘™—°‘с„о Їѕµƒє§“’÷∆≥ћљш––÷∆‘м£ђ‘ўљЂ’в–©ƒ£њйїѓµƒ¬г∆ђї•Ѕ™∆рјі£ђЌ®єэѕ»љшЈв„∞ЉЉ х£ђљЂ≤їЌђє¶ƒ№°Ґ≤їЌђє§“’÷∆‘мµƒChipletЈв„∞≥…“їЄцѕµЌ≥–Њ∆ђ£ђ“‘ µѕ÷“ї÷÷–¬–ќ љµƒ IP Єі”√°£

Chiplet µƒЄ≈ƒо‘і”Џ Marvell іі Љ»Ћ÷№–гќƒ≤© њ‘Џ ISSCC 2015 …ѕћб≥цµƒ Mochi£®Modular Chip£ђƒ£њйїѓ–Њ∆ђ£©Љ№єє£ђ∞йЋж„≈ AMD µЏ“їЄцљЂ–°–Њ∆ђЉ№єє“э»л∆д„о≥хµƒ Epyc і¶јн∆ч Naples£ђChiplet ЉЉ хњмЋўЈҐ’є°£

Ќ®єэChipletЉЉ х£ђ є”√10nmє§“’÷∆‘м≥цјіµƒ–Њ∆ђ£ђЌк»Ђ“≤њ…“‘іпµљ7nm–Њ∆ђµƒЉѓ≥…ґ»£ђµЂ «—–ЈҐЌґ»лЇЌ“їіќ–‘…ъ≤ъЌґ»л‘т±»7nm–Њ∆ђµƒЌґ»л“™…ўµƒґа£ђ–¬µƒЅђљ”–ќ љ‘Џ∆д…ъ≤ъєэ≥ћ÷–ішґѓ…и±Є–и«у°£

Chipletƒ£ љЊя±Єњ™ЈҐ÷№∆Џґћ°Ґ…иЉ∆Ѕйїо–‘«њ°Ґ…иЉ∆≥…±ЊµЌЇЌЅЉ¬ Єяµ»”≈µг°£њ…љЂ≤їЌђє§“’љЏµг°Ґ≤ƒ÷ °Ґє¶ƒ№°Ґє©”¶…ћµƒЊя”–ћЎґ®є¶ƒ№µƒ…ћ“µїѓ¬г∆ђЉѓ÷–Јв„∞°£

∆д„ч”√÷ч“™∞ьј®£ЇљµµЌµ•∆ђЊІ‘≤Љѓ≥…є§“’ЅЉ¬ Јзѕ’£ђіпµљ≥…±Њњ…њЎ£ђ”–…иЉ∆µѓ–‘£ђњ… µѕ÷–Њ∆ђґ®÷∆їѓ£їChipletљЂіу≥яізµƒґаЇЋ–ƒµƒ…иЉ∆£ђЈ÷…Ґµљљѕ–°µƒ–°–Њ∆ђ£ђЄьƒ№¬ъ„гѕ÷љсЄя–Іƒ№‘ЋЋгі¶јн∆чµƒ–и«у£їµѓ–‘µƒ…иЉ∆Јљ љ≤їљцћб…эЅйїо–‘£ђ«“њ… µѕ÷∞ьј®ƒ£њй„й„∞°Ґ–Њ∆ђЌш¬з°Ґ“мєєѕµЌ≥”л‘™ЉюЉѓ≥…ЋƒЄцЈљ√жµƒє¶ƒ№°£

ѕ»љшЈв„∞10Єц≥£Љыїщ±Њ х”пљй…№

2.5DЈв„∞

2.5DЈв„∞ «іЂЌ≥2D ICЈв„∞ЉЉ хµƒљш’є£ђњ… µѕ÷ЄьЊЂѕЄµƒѕя¬Ј”лњ’Љдјы”√°£‘Џ2.5DЈв„∞÷–£ђ¬гЊІґ—’їїт≤Ґ≈≈Ј≈÷√‘ЏЊя”–єиЌ®њ„(TSV)µƒ÷–љй≤г£®interposer£©ґ•≤њ°£∆䵄„щ£ђЉі÷–љй≤г£ђњ…ћбє©–Њ∆ђ÷ЃЉдµƒЅђљ”–‘°£2.5DЈв„∞Ќ®≥£”√”ЏЄяґЋASIC°ҐFPGA°ҐGPUЇЌƒЏіжЅҐЈљће°£2008ƒк£ђ»ьЅйЋЉ£®Xilinx£©љЂ∆діу–ЌFPGAїЃЈ÷ќ™ЋƒЄцЅЉ¬ ЄьЄяµƒљѕ–°–Њ∆ђ£ђ≤ҐљЂ’в–©–Њ∆ђЅђљ”µљєи÷–љй≤г°£2.5DЈв„∞”…іЋµЃ…ъ£ђ≤Ґ„о÷’єгЈЇ”√”ЏЄяішњнƒЏіж(HBM)і¶јн∆ч’ыЇѕ°£

3DЈв„∞

‘Џ3D ICЈв„∞÷–£ђ¬яЉ≠¬гЊІґ—’ї‘Џ“ї∆рїт”볥іж¬гЊІґ—’ї‘Џ“ї∆р£ђќё–иљ®єєіу–ЌµƒѕµЌ≥µ•–Њ∆ђ£®SoC£©°£¬гЊІ÷ЃЉдЌЄєэ÷чґѓ÷–љй≤гЅђљ”£ђ2.5D ICЈв„∞ «јы”√µЉµзЌєњйїтTSVљЂ„йЉюґ—’ї‘Џ÷–љй≤г…ѕ£ђ3D ICЈв„∞‘тљЂґа≤гєиЊІ‘≤”л≤…”√TSVµƒ„йЉюЅђљ”‘Џ“ї∆р°£TSVЉЉ х «2.5DЇЌ3D ICЈв„∞÷–µƒєЎЉь єƒ№ЉЉ х£ђ∞лµЉће≤ъ“µ“ї÷± є”√HBMЉЉ х…ъ≤ъ3D ICЈв„∞µƒDRAM–Њ∆ђ°£

Chiplet

–Њ∆ђњв÷–”–“їѕµЅ–ƒ£њйїѓ–Њ∆ђњ…“‘≤…”√¬гЊІµљ¬гЊІї•ЅђЉЉ х’ыЇѕµљЈв„∞÷–°£Chiplet «3D ICЈв„∞µƒЅн“ї÷÷–ќ љ£ђњ…“‘ µѕ÷CMOS„йЉю”лЈ«CMOS„йЉюµƒ“м÷ ’ыЇѕ£®Heterogeneous integration£©°£їїЊдї∞Ћµ£ђЋь√« «љѕ–°–ЌµƒSoC£ђ“≤љ–„цchiplet£ђґш≤ї «Јв„∞÷–µƒіу–ЌSoC°£љЂіу–ЌSoCЈ÷љвќ™љѕ–°µƒ–°–Њ∆ђ£ђ”뵕њ≈¬гЊІѕа±»Њя”–ЄьЄяµƒЅЉ¬ ЇЌЄьµЌµƒ≥…±Њ°£Chiplet є…иЉ∆»Ћ‘±њ…“‘≥дЈ÷јы”√Єч÷÷IP£ђґш≤ї”√њЉ¬«≤…”√Їќ÷÷є§“’љЏµг£ђ“‘Љ∞≤…”√Їќ÷÷ЉЉ х÷∆‘м°£Ћы√«њ…“‘≤…”√ґа÷÷≤ƒЅѕ£ђ∞ьј®єи°Ґ≤£ЅІЇЌ≤г—є∞ејі÷∆‘м–Њ∆ђ°£

…»≥ц£®Fan Out£©Јв„∞

‘Џ…»≥цЈв„∞÷–£ђ°∞Ѕђљб°±£®connection£©±ї…»≥ц–Њ∆ђ±н√ж£ђі”ґшћбє©ЄьґаµƒЌв≤њI/O°£Ћь є”√їЈ—х ч÷ђ≥…–Ќ≤ƒЅѕ£®EMC£©Ќк»Ђ«ґ»л¬гЊІ£ђ≤ї–и“™÷о»зЊІ‘≤Ќєњй°Ґ…ѕ÷ъЇЄЉЅ°Ґµє„∞–Њ∆ђ°Ґ«еља°Ґµ„≤њ≈з»ч≥дљЇЇЌєћїѓµ»є§“’Ѕч≥ћ£ђ“тіЋ“≤ќё–и÷–љй≤г£ђ є“м÷ ’ыЇѕ±дµ√ЄьЉ”Љтµ•°£”л∆дЋыЈв„∞ја–Ќѕа±»£ђ…»≥цЉЉ хћбє©ЅЋЊя”–Єьґа I/O µƒ–°≥яізЈв„∞°£2016 ƒк£ђЋь є Apple ƒ№єї є”√ћ®їэµзµƒЈв„∞ЉЉ хљЂ∆д 16 ƒ…√„”¶”√і¶јн∆ч”л“∆ґѓ DRAM Љѓ≥…µљ iPhone 7 µƒ“їЄцЈв„∞÷–£ђі”ґш≥…ќ™ЉЉ х√ч–«°£

…»≥цЊІ‘≤ЉґЈв„∞£®FOWLP£©

FOWLPЉЉ х «’лґ‘ЊІ‘≤ЉґЈв„∞£®WLP£©µƒЄƒљш£ђњ…“‘ќ™єи–Њ∆ђћбє©ЄьґаЌв≤њЅђљ”°£ЋьљЂ–Њ∆ђ«ґ»лїЈ—х ч÷ђ≥…–Ќ≤ƒЅѕ÷–£ђ»їЇу‘ЏЊІ‘≤±н√жљ®єєЄя√№ґ»÷ЎЈ÷≤Љ≤г(RDL)≤Ґ ©Љ”ЇЄќэ«т£ђ–ќ≥…÷ЎєєЊІ‘≤£®reconstituted wafer£©°£ЋьЌ®≥£ѕ»љЂЊ≠єэі¶јнµƒЊІ‘≤«–≥…µ•њ≈¬гЊІ£ђ»їЇуљЂ¬гЊІЈ÷…ҐЈ≈÷√‘Џ‘Ўћељбєє£®carrier structure£©…ѕ£ђ≤Ґћо≥дЉдѕґ“‘–ќ≥…÷ЎєєЊІ‘≤°£FOWLP‘ЏЈв„∞ЇЌ”¶”√µз¬Ј∞е÷ЃЉдћбє©ЅЋіуЅњЅђљ”£ђґш«“”…”Џїщ∞е±»¬гЊІ“™іу£ђ¬гЊІµƒЉдЊа µЉ …ѕЄьњнЋ…°£

“м÷ ’ыЇѕ

љЂЈ÷њ™÷∆‘мµƒ≤їЌђ„йЉю’ыЇѕµљЄьЄяЉґ±рµƒ„йЉю÷–£ђњ…“‘‘ц«њє¶ƒ№≤ҐЄƒљшє§„чћЎ–‘£ђ“тіЋ∞лµЉће„йЉю÷∆‘м…ћƒ№єїљЂ≤…”√≤їЌђє§“’Ѕч≥ћµƒє¶ƒ№„йЉю„йЇѕµљ“їЄц„йЉю÷–°£“м÷ ’ыЇѕјаЋ∆”ЏѕµЌ≥ЉґЈв„∞£®SiP£©£ђµЂЋь≤Ґ≤ї «љЂґањ≈¬гЊІ’ыЇѕ‘Џµ•Єцїщ∞е…ѕ£ђґш «љЂґаЄцIP“‘Chipletµƒ–ќ љ’ыЇѕ‘Џµ•Єцїщ∞е…ѕ°£“м÷ ’ыЇѕµƒїщ±ЊЋЉѕл «љЂґаЄцЊя”–≤їЌђє¶ƒ№µƒ„йЉю„йЇѕ‘ЏЌђ“їЄцЈв„∞÷–°£

HBM

HBM «“ї÷÷±к„Љїѓµƒґ—’їіҐіжЉЉ х£ђњ…ќ™ґ—’їƒЏ≤њ£ђ“‘Љ∞ƒЏіж”л¬яЉ≠„йЉю÷ЃЉдµƒ эЊЁћбє©Єяішњн–≈µј°£HBMЈв„∞љЂƒЏіж¬гЊІґ—’ї∆рјі£ђ≤ҐЌЄєэTSVљЂЋь√«Ѕђљ”‘Џ“ї∆р£ђі”ґшііљ®ЄьґаµƒI/OЇЌішњн°£HBM «“ї÷÷JEDEC±к„Љ£ђЋь‘ЏЈв„∞ƒЏіє÷±’ыЇѕЅЋґа≤гDRAM„йЉю£ђЈв„∞ƒЏїє”–”¶”√і¶јн∆ч°ҐGPUЇЌSoC°£HBM÷ч“™“‘2.5DЈв„∞µƒ–ќ љ µѕ÷£ђ”√”ЏЄяґЋЈюќс∆чЇЌЌш¬з–Њ∆ђ°£ѕ÷‘ЏЈҐ≤ЉµƒHBM2∞ж±ЊљвЊцЅЋ≥х ЉHBM∞ж±Њ÷–µƒ»ЁЅњЇЌ ±÷”Ћў¬ ѕё÷∆ќ ћв°£

÷–љй≤г

÷–љй≤г «Јв„∞÷–ґа–Њ∆ђ¬гЊІїтµз¬Ј∞еіЂµЁµз–≈Ї≈µƒє№µј£ђ «≤ењЏїтљ”ЌЈ÷ЃЉдµƒµзљ”њЏ£ђњ…“‘љЂ–≈Ї≈іЂ≤•Єь‘ґ£ђ“≤њ…“‘Ѕђљ”µљ∞е„”…ѕµƒ∆дЋы≤ењЏ°£÷–љй≤гњ…“‘”…єиЇЌ”–їъ≤ƒЅѕ÷∆≥…£ђ≥дµ±ґањ≈¬гЊІЇЌµз¬Ј∞е÷ЃЉдµƒ«≈ЅЇ°£єи÷–љй≤г «“ї÷÷Њ≠єэ—й÷§µƒЉЉ х£ђЊя”–љѕЄяµƒѕЄЉдЊаI/O√№ґ»ЇЌTSV–ќ≥…ƒ№Ѕ¶£ђ‘Џ2.5DЇЌ3D IC–Њ∆ђЈв„∞÷–∞з—Ё„≈єЎЉьљ«…Ђ°£

÷ЎЈ÷≤Љ≤г

÷ЎЈ÷≤Љ≤г∞ьЇђЌ≠Ѕђљ”ѕяїт„яѕя£ђ”√”Џ µѕ÷Јв„∞ЄчЄц≤њЈ÷÷ЃЉдµƒµз∆шЅђљ”°£Ћь «љр фїтЄяЈ÷„”љйµз≤ƒЅѕ≤г£ђ¬гЊІњ…“‘ґ—’ї‘ЏЈв„∞÷–£ђі”ґшЋх–°іу–Њ∆ђ„йµƒI/OЉдЊа°£÷ЎЈ÷≤Љ≤г“—≥…ќ™2.5DЇЌ3DЈв„∞љвЊцЈљ∞Є÷–≤їњ…їт»±µƒ“ї≤њЈ÷£ђ є∆д…ѕµƒ–Њ∆ђњ…“‘јы”√÷–љй≤гѕаї•љш––Ќ®—ґ°£

TSV

TSV «2.5DЇЌ3DЈв„∞љвЊцЈљ∞ЄµƒєЎЉь µѕ÷ЉЉ х£ђ «‘ЏЊІ‘≤÷–ћо≥дЌ≠£ђћбє©єбЌ®єиЊІ‘≤¬гЊІµƒіє÷±ї•Ѕђ°£Ћьєбі©’ыЄц–Њ∆ђ“‘ћбє©µз∆шЅђљ”£ђ–ќ≥…і”–Њ∆ђ“ї≤аµљЅн“ї≤аµƒ„оґћ¬ЈЊґ°£і”ЊІ‘≤µƒ’э√жљЂЌ®њ„їтњ„ґі іњћµљ“їґ®…оґ»£ђ»їЇуљЂ∆дЊш‘µ£ђ≤Ґ≥ЅїэµЉµз≤ƒЅѕ£®Ќ®≥£ќ™Ќ≠£©љш––ћо≥д°£–Њ∆ђ÷∆‘мЌк≥…Їу£ђі”ЊІ‘≤µƒ±≥√жљЂ∆дЉх±°£ђ“‘±©¬ґЌ®њ„ЇЌ≥Ѕїэ‘ЏЊІ‘≤±≥√жµƒљр ф£ђі”ґшЌк≥…TSVї•Ѕђ°£

°ш „Ґ£Їќƒ’¬Љ∞ЌЉ∆ђ’ыјн„™‘Ў”ЏЌш¬з£ђљцє©≤ќњЉ—Іѕ∞£ђ∞ж»®єй‘≠„ч’яЋщ”–£ђ»з…жЉ∞«÷»®£ђ«лЅ™ѕµ–°±а…Њ≥э°£

Pre£Ї ≤√і «іҐƒ№ƒж±д∆ч£њіҐƒ№ƒж±д∆чЇЌєвЈьƒж±д∆чµƒ«ш±р « ≤√і£њ 2026-05-08

Next£Ї“‘…ЂЅ–£ђѕ ќ™»Ћ÷™µƒ–Њ∆ђЌхєъ 2026-05-08

Collect

Collect

Navigate£Ї

Navigate£Ї