SLA7060M-SLA7061M-SLA7062M-SLA7065M-SLA7066M-SLA7067M

DATASHEET PDF![]() 7060.pdf

7060.pdf

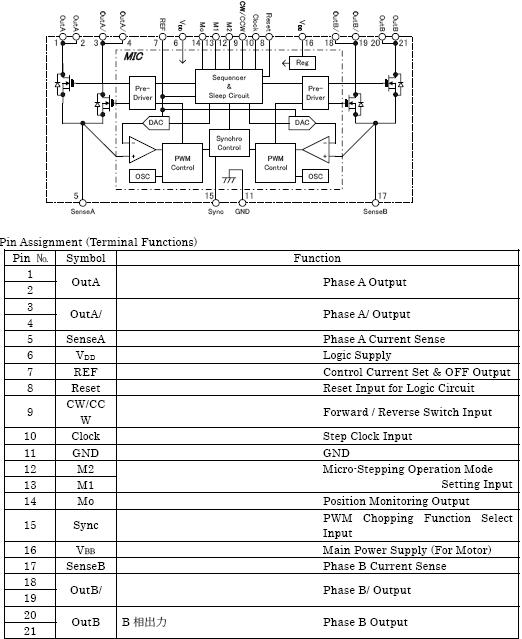

■General Description

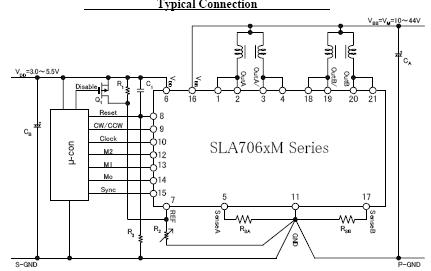

Combining low-power CMOS logic with high-current, high-voltage

power FET outputs, the Series SLA706xM translator/drivers provide

complete control and drive for a two-phase unipolar stepper motor

with internal fixed off time and pulse-width modulation (PWM)

control of the output current in a power multi-chip module

(PMCM™).

There are no phase-sequence tables, high-frequency control lines,

orcomplex interfaces to program.The CMOS logic section provides

the sequencing logic, direction,control, synchronous/asynchronous

PWM operation, and a "sleep"function. The minimum CLOCK input

is an ideal fit for applications where a complex µP is unavailable or

overburdened. TTL or LSTTL may require the use of appropriate

pull-up resistors to ensure a proper input-logic high. For PWM current

control, the maximum output current is determined by the user's

selection of a reference voltage and sensing resistor. The NMOS

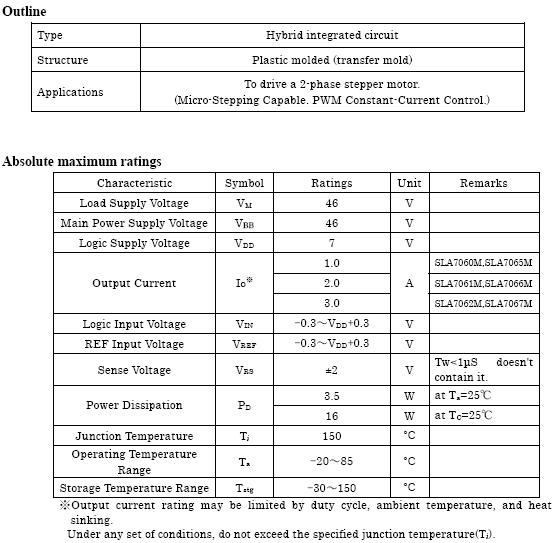

outputs are capable of sinking up to 1, 2, or 3 A (depending on device)

and withstanding 46 V in the off state.

Clamp diodes provide protection against inductive transients. Special

power-up sequencing is not required.

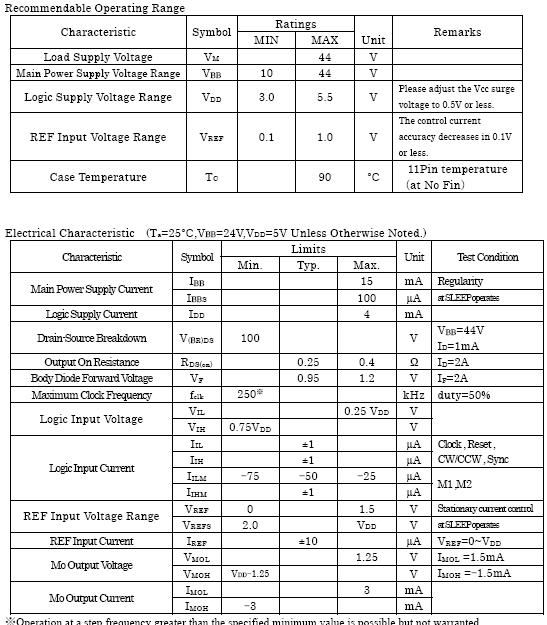

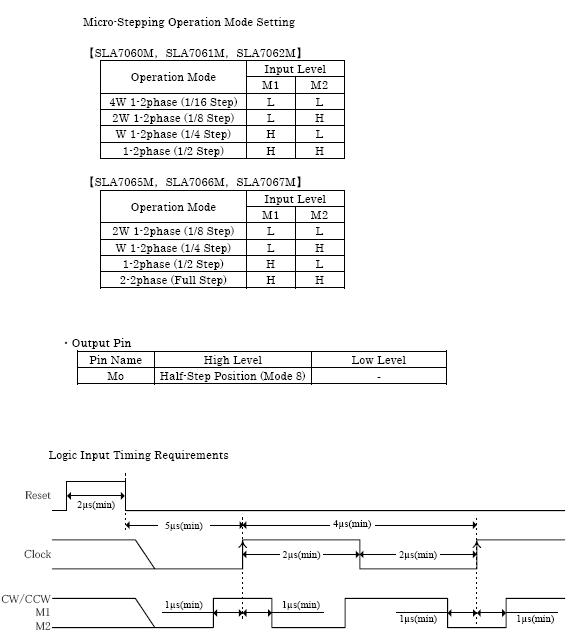

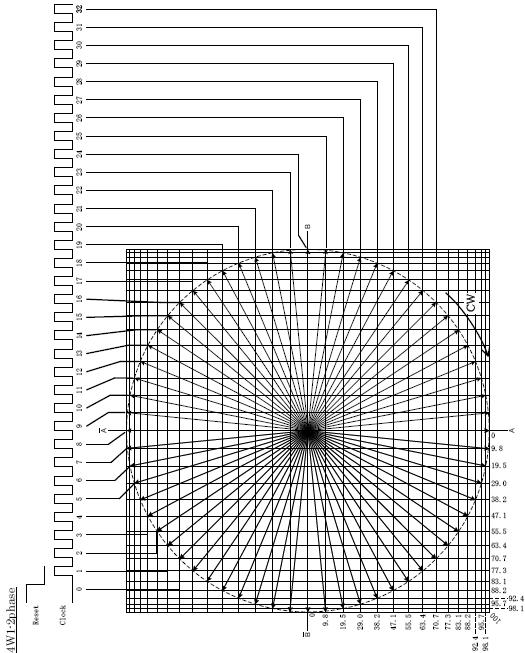

Half-, quarter-, eighth-, and sixteenth-step operation are externally

selectable for the SLA7060/61/62M. Full-, Half-, quarter-, and

eighth-step operation are externally selectable for the

SLA7065/66/67M.

Half-step excitation alternates between the one-phase and two-phase

modes (A-AB-B-AB-A-AB-BAB),providing an eight-step sequence

上一篇:SLA7042M and SLA7044M 技术资料及报价(附PDF文档) 2026-04-08

下一篇:SLA7032M and SLA7033M 技术资料及报价(附PDF文档) 2026-04-08

收藏本站

收藏本站

当前位置:

当前位置: